Een virtualisatieraamwerk voor ingebedde systemen

A Virtualisation Framework for Embedded Systems

Niels Penneman

Promotoren: prof. dr. ir. K. De Bosschere, prof. dr. ir. B. De Sutter Proefschrift ingediend tot het behalen van de graad van Doctor in de Ingenieurswetenschappen: Computerwetenschappen

Vakgroep Elektronica en Informatiesystemen Voorzitter: prof. dr. ir. R. Van de Walle Faculteit Ingenieurswetenschappen en Architectuur Academiejaar 2015 - 2016

ISBN 978-90-8578-861-4 NUR 980 Wettelijk depot: D/2015/10.500/105

Brevis esse laboro, obscurus fio. – Q. Horatii Flacci Ars Poetica.

## Acknowledgements

This book tells the story of a journey that started over 6 years ago, when I was still completing my Masters degree at the Vrije Universiteit Brussel. I had gathered a fair bit of knowledge on the basics of electrical engineering in my Bachelor studies, but my all-time passion had driven me to pursue a Master in Applied Computer Science Engineering instead. Striving to combine my knowledge of both domains, I quickly gained interest in embedded systems, partly thanks to a course on operating systems taught by prof. Martin Timmerman. I was lucky to have a flexible curriculum that allowed me to pick several elective courses on topics related to embedded systems in the final year of my Masters programme. It was in one of those courses that I met prof. Bjorn De Sutter from Ghent University, whom I had very interesting discussions with. Close to the end of his course, we talked about research opportunities in the fields of compilation and virtualisation techniques for embedded systems.

I had been interested in virtualisation in the context of desktop systems and cloud computing for a while, and the thought of using virtualisation techniques on embedded systems was relatively new to me. I had previously considered cloud computing as a topic for my Masters thesis, but I eventually chose an entirely different subject. I realised that the limited amount of time given to complete such a thesis would be too short for me to create anything practically useful—and I really wanted to *create* something that was preferably both novel and useful.

Despite my interest in virtualisation, I was not immediately convinced that pursuing a Ph.D. was the right choice for me. My doubts, however, quickly vanished after a motivational talk with prof. Koen De Bosschere at Ghent University, and so I plunged into this adventure. Both Bjorn and Koen became my supervisors, and over the years this tandem has worked rather well. They helped me to obtain a grant for my research, and they have provided me with guidance and motivation in times of need. I would therefore like to thank my supervisors, Bjorn and Koen, for their continued efforts. I would also like to thank prof. Dirk Vermeir of the Vrije Universiteit Brussel, and prof. Martin Timmerman of the Royal Military Academy, for providing me with pointers and insights that sparked my interest in embedded systems and virtualisation.

In the early days, when I was still determining my research topic, I met prof. Alasdair Rawsthorne from The University of Manchester for a discussion on embedded virtualisation. Little did I know at that time that this would be the start of our cooperation, which has lasted for several years, and through which I obtained the basic knowledge on hypervisors. I was later introduced to two of his students in Manchester, Danielius Kudinskas and Alex Merrick, who started a Bachelor project to virtualise ARM-based embedded systems using dynamic binary translation. During the next few years I worked together with Danielius to create the hypervisor that would form the basic platform for my research. I would therefore like to thank prof. Alasdair Rawsthorne, Danielius Kudinskas and Alex Merrick for their valuable input and contributions.

Furthermore, I would also like to thank the other members of my examination board for their time and their valuable feedback: dr. Jonas Maebe, prof. Wilfried Philips and prof. Luc Taerwe. Additionally I would like to thank Luc Perneel for his detailed reviews of my work.

The first four years of my research were funded by the agency for Innovation by Science and Technology (IWT) by means of a personal research grant. Afterwards, I contributed to and obtained results in the context of the EURO-MILS project, which was funded by the European Union's Seventh Framework Programme under grant agreement number ICT-318353. I would therefore like to thank the IWT and all people involved in getting the EURO-MILS project get off the ground.

Throughout those years, several Master students have contributed to my research project as a part of their thesis: Sarah Tawfik Adel El Shal from the Vrije Universiteit Brussel [51]; Peter Van Bouwel [129], Henri De Veene [43] and Jens Van den Broeck [130] from Ghent University; and Markos Chandras [31] and Cosmin Gorgovan from The University of Manchester. Even though not all of their contributions made it into the final version of the hypervisor developed as part of my research, they have provided me with useful insights. Guiding the students in Brussels and Ghent was a valuable experience for me. Additional thanks go out to Wim Meeus for his assistance in guiding Jens, and to prof. Pieter Rombouts for providing us with the necessary equipment.

I would also like to thank ARM for providing the high-end development tools that made my life a lot easier when developing and debugging the hypervisor. ARM has also provided excellent support for their tools, from helping to get them to cooperate with officially unsupported hardware, to responding to and ultimately implementing our feature requests, even though we were only a small customer on a discounted contract.

While I have spent most of my time working alone, I was happy to find myself surrounded by a number of colleagues that made my work more bearable. Panagiotis, no one has given me as much motivation to go on as you did. Over the years we have become good friends, and we have had fun together both in Ghent and in several places abroad. You have inspired me on several occasions and in several activities unrelated to work, from photography to our workouts at the gym. Even though you will soon be returning to Greece, I hope that we will keep in touch.

Christophe and Jeroen, it was fun to have you around, and to cruise through Greece together to attend Panagiotis' wedding. I would also like to thank you for leaving our office mostly empty until noon, so that I could work without disturbances (and play music on the big speakers).

Bart, the same goes for you. As you started your Ph.D. a few years before me, you were a reliable source of non-technical information concerning the whole process. Your experience came in handy to fix my uncertainties while going through the final phases of my Ph.D.

Jonas, thanks again for sharing your experiences with me on the ARM architecture from the very beginning, and for staying calm even in the most frustrating situations we had in the EURO-MILS project.

Tim and Jens, we have spent a lot of time together with Panagiotis to teach and prepare introductory labs on electronics. At times this was fun, but we also shared quite some frustrations. Luckily, we all managed to keep our sanity, because we made a great and competent team that did not struggle to divide the workload—unlike some of our students.

Stijn, thanks for your input on low-level programming and reverse engineering. I have learnt a few useful things in your ethical hacking sessions. Bert, Farhadur, Hadi, Ronald, Peng, Sander and Wim, even though we had less interactions, it was nice to have you around nonetheless.

Marnix, you helped us to set up the lab, you kept track of equipment orders, and so much more. I am still amazed at how much work you manage to do in one day. Together with Vicky, you took a lot of administrative work out of my hands. Thanks for all your efforts. Ronny, Michiel, and Klaas, thanks for being there whenever we had a problem with our IT infrastructure and those dreadful Drupal-based websites.

At the end of February 2015, I left Ghent University to start working for Televic. I was still finalising my thesis and my second journal paper. It was not an obvious task to do this after normal working hours, but luckily I ended up working in a stimulating environment, with people that provided me with moral support to finish my Ph.D. I would therefore also like to thank my colleagues and former colleagues at Televic.

Pursuing a Ph.D. is not a nine-to-five job. We were all given the freedom to start and stop working whenever we wanted. We could work from home if we wanted. In the end, though, we needed to deliver results so that we could eventually complete our research. We were given an informal deadline of four years, as most research grants—at least in our domain—typically cover four years. When you are working on a personal grant, you are mostly working for yourself. The more you get done in a day, the closer you get to finishing your Ph.D. It does not matter when you step outside the office and close the door behind you. Your research is stuck in the back of your mind, and you take it with you wherever you go. You go to bed with it, and you wake up with it. It changes you and the way you interact with the people close to you.

My parents have, without doubt, taken the majority of my frustrations. They have nevertheless motivated me to continue over and over again. They have done a lot for me only so that I would have more time to work on my research. Without their support, I would never have managed. I would also like to thank Mark and Magda. Having them around is almost like having an extra pair of parents—even though they have quite a different view on life, but that is part of the fun. I thank them for supporting me, for proofreading, and for everything else! Further thanks go to Martine and Jan, because they made time to support me and to have fun together even in difficult circumstances.

I would also like to thank my friends for bearing with me and supporting me up until today. I will not try to provide an exhaustive list of all their names. You know who you are, and please understand that I have really appreciated all your support. Special thanks go out to Magalie, for all the fun she has brought me on our time together in South Africa, the Netherlands, and here in Belgium, and for the support she has given me whenever I needed it, even when we could not physically be together. Karolien, thank you for being there whenever I needed someone to talk to. Davy, Thierry, Jens, Freija, Bruno, Farid, Ilse, ... you all helped me to keep my sanity throughout this journey. Thank you!

> Niels Penneman Ghent, 7 December 2015

### Examencommissie

- Prof. Luc Taerwe, *voorzitter* Vakgroep Bouwkundige Constructies Faculteit Ingenieurswetenschappen en Architectuur Universiteit Gent

- Dr. Jonas Maebe, *secretaris* Vakgroep Elektronica en Informatiesystemen Faculteit Ingenieurswetenschappen en Architectuur Universiteit Gent

- Prof. Koen De Bosschere, promotor Vakgroep Elektronica en Informatiesystemen Faculteit Ingenieurswetenschappen en Architectuur Universiteit Gent

- Prof. Bjorn De Sutter, promotor Vakgroep Elektronica en Informatiesystemen Faculteit Ingenieurswetenschappen en Architectuur Universiteit Gent

- Prof. Wilfried Philips Vakgroep Telecommunicatie en Informatieverwerking Faculteit Ingenieurswetenschappen en Architectuur Universiteit Gent

- Em. Prof. Alasdair Rawsthorne School of Computer Science Faculty of Engineering and Physical Sciences The University of Manchester

- Prof. Martin Timmerman Departement Wiskunde Faculteit Polytechniek Koninklijke Militaire School

# Leescommissie

- Prof. Wilfried Philips Vakgroep Telecommunicatie en Informatieverwerking Faculteit Ingenieurswetenschappen en Architectuur Universiteit Gent

- Em. Prof. Alasdair Rawsthorne School of Computer Science Faculty of Engineering and Physical Sciences The University of Manchester

- Prof. Martin Timmerman Departement Wiskunde Faculteit Polytechniek Koninklijke Militaire School

## Samenvatting

Systeemvirtualisatie ontkoppelt een besturingssysteem van de hardware van een fysieke machine door middel van een hypervisor. Het besturingssysteem wordt dan ook een *gast* genoemd. Systeemvirtualisatie heeft al verschillende toepassingen gevonden in de desktop- en serverwereld, gaande van het reduceren van de operationele kosten van datacenters door het consolideren van servers, tot het vergemakkelijken van softwareontwikkeling en het emuleren van software voor verouderde hardware. Ingebedde systemen worden alsmaar krachtiger, en hun hardware evolueert sneller dan hun software. Daarom worden deze systemen nu ook interessant om te virtualiseren. De bestaande technieken voor servers en desktops kunnen echter niet zomaar worden gebruikt voor ingebedde systemen, omdat deze vaak andere vereisten, andere toepassingen en andere architecturen hebben dan servers en desktops.

ARM is met ruime voorsprong de marktleider voor processors van ingebedde systemen en in het bijzonder van mobiele toestellen. In het voorbije decennium werden reeds verschillende hypervisors ontwikkeld voor de ARM-architectuur. Omdat deze architectuur echter geen ondersteuning kon bieden voor volledige virtualisatie, steunt de meerderheid van de bestaande hypervisors op paravirtualisatie, een techniek met veel nadelen. ARM heeft onlangs zijn ARMv7-A-architectuur uitgebreid met hardware-ondersteuning voor volledige virtualisatie. Hoewel hypervisors die van deze uitbreidingen gebruik maken niet dezelfde nadelen met zich meebrengen als hypervisors gebaseerd op paravirtualisatie, kunnen ze niet werken op de meerderheid van de ARM processors die momenteel in omloop zijn, omdat deze processors nog niet beschikken over de uitbreidingen voor volledige virtualisatie. Softwaregebaseerde technieken zoals dynamisch binaire vertaling (DBV) bieden een alternatieve oplossing om architecturen die vanuit de hardware geen volledige virtualisatie ondersteunen toch volledig te virtualiseren: problematische instructies in de binaire code van de gastbesturingssystemen worden tijdens het uitvoeren herschreven. DBV is veelzijdiger dan hardwareuitbreidingen voor volledige virtualisatie, aangezien het inherent heel wat meer toepassingen biedt, gaande van het optimaliseren tussen besturingssystemen en applicaties, het emuleren en optimaliseren van verouderde softwarestapels, het beïnstrumenteren en testen van volledige softwarestapels tot zelfs het optimaal verdelen van de werklasten in heterogene multikernprocessors door het vertalen van binaire code over de verschillende architecturen heen.

De belangrijkste onderzoeksvraag die we in deze doctoraatsthesis wensen te behandelen is: welke technologische uitdagingen moeten overwonnen worden om deze toepassingen van DBV mogelijk te maken op de ARMv7-A architectuur? Als eerste stap om een antwoord te formuleren op deze vraag, onderzoeken we welke beperkingen de architectuur oplegt die volledige virtualisatie belemmeren. We stellen vervolgens generieke softwaretechnieken voor om de processor en het geheugenbeheer volledig te virtualiseren zonder gebruik te maken van de nieuwe hardware-uitbreidingen voor de ARMv7-A-architectuur. Voor de virtualisatie van het geheugenbeheer zullen we ons onderzoek toespitsen op technieken die gebruik maken van schaduwpaginatabellen.

We beginnen bij de theorie van klassieke virtualiseerbaarheid van Popek en Goldberg. We breiden hun theorie uit voor moderne RISCarchitecturen (reduced instruction set computer) en moderne toepassingen: we voegen formalismen toe voor virtueel geheugen met paginatabellen, invoer en uitvoer, en onderbrekingen. We gebruiken vervolgens deze uitgebreide theorie om te analyseren waarom de oorspronkelijke ARMv7-A-architectuur niet klassiek virtualiseerbaar is, en hoe de recente hardware-uitbreidingen van ARM de architectuur wél virtualiseerbaar maken. Vertrekkend vanuit het standpunt dat hypervisors gebaseerd op dynamisch binaire vertaling in principe een evolutie zijn van de ideeën van Popek en Goldberg over hybride virtualisatie, tonen we aan hoe onze uitgebreide theorie helpt bij het construeren van een dynamisch binaire vertaler voor volledige systeemvirtualisatie.

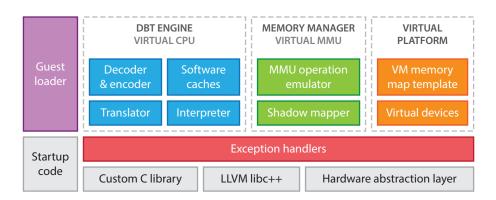

We gebruiken onze analyse als basis voor het ontwerp van de *STAR hypervisor*, een nieuwe bare-metal hypervisor voor de ARMv7-A-architectuur. Onze hypervisor is de eerste open source hypervisor voor de ARMv7-A-architectuur dat een systeem volledige kan virtualiseren door uitsluitend gebruik te maken van softwaretechnieken. Besturingssystemen kunnen zonder wijzigingen als gast uitgevoerd worden bovenop

deze hypervisor, volledig afgeschermd van de fysieke CPU door DBV, en van de fysieke MMU door middel van schaduwpaginatabellen.

Bestaand werk omtrent DBV voor de ARM-architectuur richt zich vooral op procesvirtualisatie. Systeemvirtualisatie heeft zijn eigen unieke uitdagingen, waardoor technieken voor procesvirtualisatie niet zomaar kunnen worden overgenomen in een hypervisor voor systeemvirtualisatie. Dynamisch binaire vertalers voor procesvirtualisatie gaan er vaak van uit dat de applicaties die gevirtualiseerd worden zich steeds correct gedragen. Bovendien is het vaak niet belangrijk om de vertaler en de vertaalde applicatie strikt van elkaar te scheiden. Bij volledige systeemvirtualisatie is een correcte vertaling echter essentieel om de afscherming tussen de gast, de hypervisor, en de fysieke hardware te garanderen. De hypervisor kan geen enkele aanname maken over het gedrag van een gastbesturingssysteem, omdat de code van besturingssysteemkernen vaak handgeschreven instructiesequenties en gespecialiseerde systeeminstructies bevatten die bijzondere aandacht vereisen bij de vertaling.

We bestuderen hoe we de uitdagingen aan DBV voor volledige systeemvirtualisatie moeten aanpakken, uitgaande van een fundamenteel probleem bij de vertaling van binaire code: onze vertalingen hebben vaak een extra register nodig om tijdelijk informatie op te slaan, maar het is niet altijd mogelijk om een register te vinden dat vrij kan worden gebruikt. Onze vertaler moet daarom een register vrijmaken door tijdelijk de waarde van dat register elders op te slaan, en na gebruik deze waarde terug te herstellen. De opslagplaats moet bovendien toegankelijk zijn voor de vertaalde code van het gastbesturingssysteem. Dit probleem is heel eenvoudig op te lossen bij procesvirtualisatie. Bij systeemvirtualisatie is dit echter veel moeilijker, mede omdat de hypervisor zoveel mogelijk zijn eigen geheugen moet afschermen van het gastbesturingssysteem. Bovendien kan de hypervisor geen aannames maken over de inhoud van het geheugen van het gastbesturingssysteem. We stellen nieuwe oplossingen voor die deze problematiek aanpakken, en we evalueren hun impact op de uitvoeringstijd van vertaalde code.

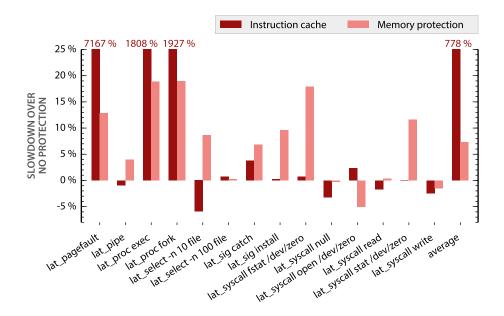

Daarna bepalen we hoe we de vertaalde code verder kunnen optimaliseren. We trachten de oorzaak van de kosten verbonden aan de vertaling te identificeren aan de hand van metingen met micro-benchmarks uit van de Imbench suite. Deze benchmarks staan model voor typische interacties tussen de gebruikersapplicaties en de besturingssysteemkern voor Linux-gebaseerde besturingssystemen. We bestuderen welke instructies het vaakst een tussenkomst van de hypervisor vergen in vertaalde code in elk van deze benchmarks. Vervolgens stellen we vertaaltechnieken voor die deze tussenkomsten zo veel mogelijk elimineren, en we evalueren de impact van elke nieuwe techniek op elke benchmark afzonderlijk. Zoals wel vaker het geval is bij DBV, valt op dat instructies die het controleverloop bepalen voor de grootste vertraging in uitvoeringstijd zorgen. Voor deze instructies kunnen bestaande technieken worden aangewend, met significante prestatieverbeteringen tot gevolg. We merken echter op dat onze optimalisaties specifiek voor volledige systeemvirtualisatie de resterende vertraging nog met gemiddeld 51% kunnen reduceren.

We bekijken vervolgens de impact van onze vertaaltechnieken op echte applicaties. We voeren benchmarks uit van de mibench suite die het gedrag van realistische applicaties modelleren. We vergelijken de uitvoeringstijd van deze benchmarks op een ongevirtualiseerd systeem, met de uitvoeringstijd op de oorspronkelijke versie van onze vertaler, en de uitvoeringstijd op de geoptimaliseerde vertaler. Onze metingen tonen aan dat applicaties tot 5 keer vertraagd worden door de oorspronkelijke vertaler. De geoptimaliseerde vertaler beperkt de vertraging van realistische applicaties tot slechts 39% in het slechtste geval.

De vertaler van de hypervisor staat enkel in voor CPU-virtualisatie. De hypervisor moet daarnaast ook nog het geheugenbeheer, de fysieke caches en de translation lookaside buffers (TLBs) virtualiseren. We beschrijven welke technieken we gebruiken om het geheugenbeheer te virtualiseren door middel van schaduwpaginatabellen, en hoe we cacheoperaties virtualiseren. We zien onder andere dat cacheoperaties van gastbesturingssystemen niet zomaar kunnen uitgevoerd worden op de fysieke caches, omdat de hypervisor hierdoor gegevens kan verliezen.

Onze hypervisor maakt gebruik van diverse softwarecaches, zowel in de vertaler als in de virtualisatie van het geheugenbeheer. De gegevens in deze softwarecaches moeten ten allen tijde overeenkomen met de interne toestand van het gastbesturingssysteem waarop ze betrekking hebben. De hypervisor kan dit probleem op twee verschillende manieren aanpakken. Een eerste aanpak steunt op geheugenbeheer: de interne toestand van de gast die interessant is voor het beheer van de caches wordt beschermd tegen schrijfoperaties van de gast, zodat de hypervisor weet wanneer de gast zijn interne toestand wijzigt. Een tweede aanpak koppelt het beheer van de softwarecaches aan hoe de gast de hardwarecaches probeert aan te sturen. De softwarecaches worden dan als het ware een gevirtualiseerde hardwarecache voor de gast.

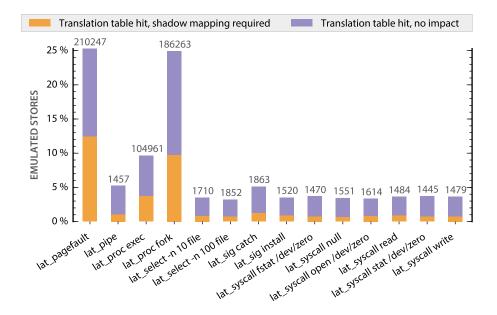

De caches van de vertaler moeten bijgewerkt worden telkens wanneer

een gast zijn code bewerkt, verplaatst of verwijdert. De caches van het gevirtualiseerd geheugenbeheer, nl. de schaduwpaginatabellen, moeten op gelijkaardige manier worden onderhouden: telkens wanneer een gast zijn eigen paginatabellen aanpast, moet onze hypervisor de schaduwpaginatabellen ook aanpassen. Aangezien we een lui mechanisme gebruiken om de schaduwpaginatabellen in te vullen, hoeven we enkel die delen te onderhouden die reeds ingevuld werden.

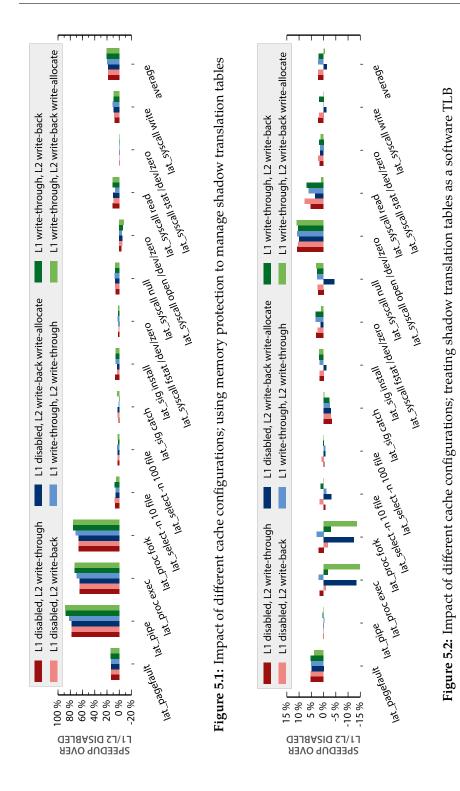

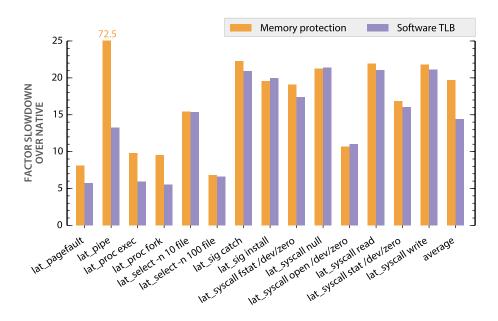

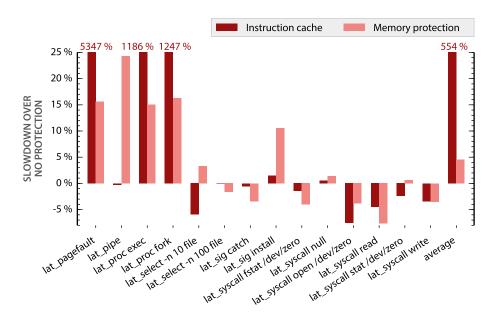

We hebben zowel voor het beheer van de caches van de vertaler als voor de schaduwpaginatabellen de twee beschreven technieken geïmplementeerd en geëvalueerd. Uit onze metingen concluderen we dat we het beheer van de schaduwpaginatabellen op ARM best koppelen aan het TLB-beheer van de gast. De caches van de vertaler worden echter beter beheerd door gebruik te maken van geheugenbescherming. Dit is een rechtstreeks gevolg van de manier waarop de fysieke TLB en caches georganiseerd zijn in de ARMv7-A-architectuur.

Tijdens ons onderzoek hebben we een virtualisatieplatform ontwikkeld voor de ARMv7-A-architectuur, waarop alle bovenvermelde technieken geïmplementeerd en geëvalueerd werden. We hebben aangetoond dat het gebruik van DBV voor processorvirtualisatie aanvaardbare virtualisatiekosten met zich meebrengt, zolang de juiste optimalisaties aangewend worden. We hebben aangetoond hoe het geheugenbeheer volledig kan worden gevirtualiseerd, enkel gebruik makend van softwareoplossingen. We hebben verschillende technieken voorgesteld en getest om de nodige softwarecaches te beheren, en de beste technieken voor elke cache afzonderlijk vastgelegd. Ons onderzoek heeft dus de fundamentele uitdagingen opgelost om softwaregebaseerde virtualisatie met DBV mogelijk te maken op de ARMv7-A-architectuur.

# Summary

In system virtualisation, an operating system is isolated from the hardware of a physical machine by means of a hypervisor. Such an operating system is then called a *guest* of that hypervisor. System virtualisation has already proven itself to be useful in many cases ranging from reducing operational costs of data centres through consolidation, to facilitating software development and emulating legacy software. So far, however, virtualisation has mainly been used on desktops and servers. As embedded systems are growing more powerful, and embedded hardware is evolving faster than software, embedded systems can now also benefit from virtualisation. Existing solutions for data centres and desktop computers can, however, not be readily applied to embedded systems, because of differences in requirements, use cases, and architecture.

ARM is by far the leading architecture in the embedded and mobile market. Over the past decade multiple hypervisors have been developed for it. Because the ARM architectures did not support full system virtualisation, most efforts started with paravirtualisation, a technique known to have several drawbacks. Recently, ARM extended its ARMv7-A architecture with hardware support for full virtualisation. While hypervisors using these extensions do not suffer from the drawbacks of paravirtualisation, they cannot run on the vast majority of ARM processors in use today, due to their need for special hardware support. Alternatively, architectures that do not support full virtualisation out of the box can be virtualised using dynamic binary translation (DBT) techniques: problematic instructions are patched at run time in the binary instruction stream of the guest. DBT is more versatile than architectural support for full virtualisation, as it transparently enables a multitude of other virtualisation usage scenarios such as optimisations across the border between operating system kernels and applications, emulation and optimisation of legacy software stacks, full system instrumentation and

testing, and even load balancing in heterogeneous multi-core systems through cross-architecture virtualisation.

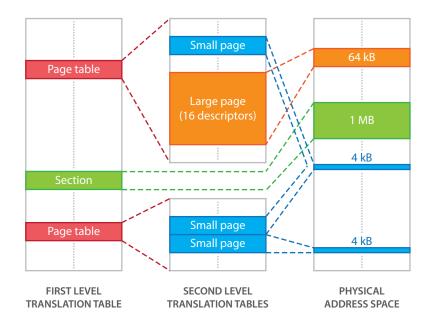

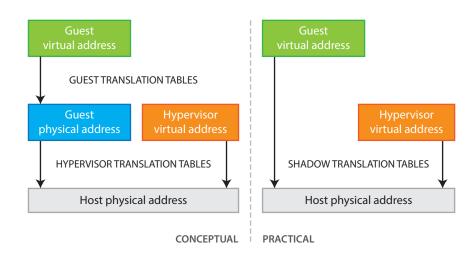

The key research question we seek to address is: which technological challenges must be solved to enable the above mentioned use cases for DBT on the ARMv7-A architecture? To answer this question, we first identify the architecture's limitations to full system virtualisation. We then propose generic CPU and memory virtualisation solutions that offer full virtualisation without relying on specific hardware support for the ARMv7-A architecture. Our research on software-only memory virtualisation techniques will focus on shadow translation tables.

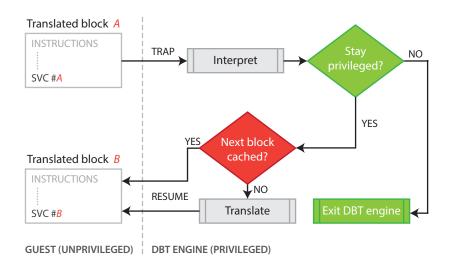

We start from Popek and Goldberg's classic virtualisability theory, and extend it for today's reduced instruction set computer (RISC) architectures and usage patterns: we add paged virtual memory, input/output (IO), and interrupts. We then use our updated model to show why the original ARMv7-A architecture is not classically virtualisable, and how ARM's hardware extensions make it virtualisable. We argue that DBT-based hypervisors are an evolution of Popek and Goldberg's ideas on hybrid virtualisation, and we show how our updated model can assist with the construction of a DBT engine for full system virtualisation.

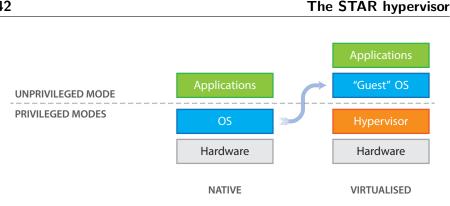

We use our analysis to build the *STAR hypervisor*, a new bare-metal hypervisor for the ARMv7-A architecture. Our hypervisor is the first open-source software-only hypervisor for the ARMv7-A architecture that offers full system virtualisation. It runs unmodified guest operating systems, decoupled from the hardware through DBT, and uses shadow translation tables to virtualise the memory management unit (MMU).

Prior work on DBT for the ARM architecture mainly focuses on process virtualisation. As system virtualisation comes with its own unique challenges, the existing process virtualisation techniques cannot be used "as is" in the context of full system virtualisation. In user-space, DBT engines often take shortcuts which are only valid for well-behaving applications, and there is no strict requirement to isolate the DBT engine from the application. In full system virtualisation, DBT is used together with MMU virtualisation to isolate guests from the hypervisor and from one another. Furthermore, kernel code often contains handwritten assembly and special system instructions, requiring special care in the DBT engine.

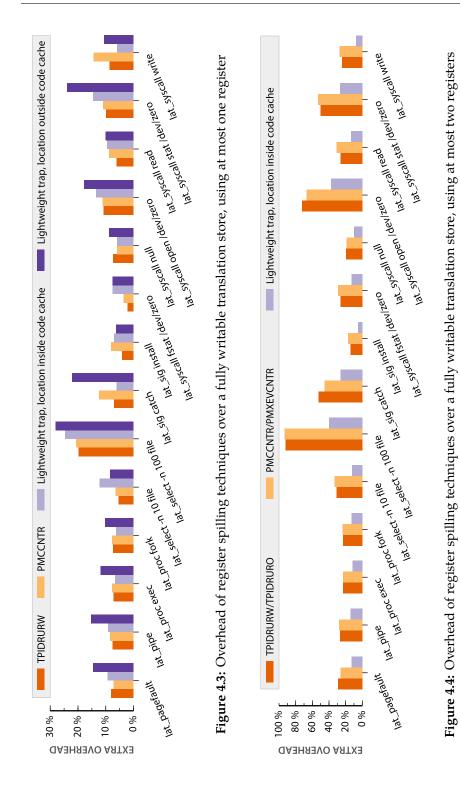

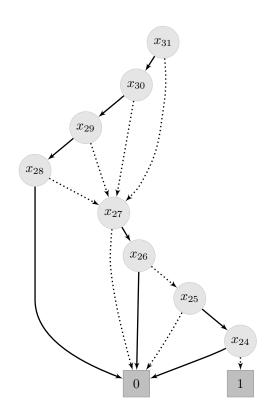

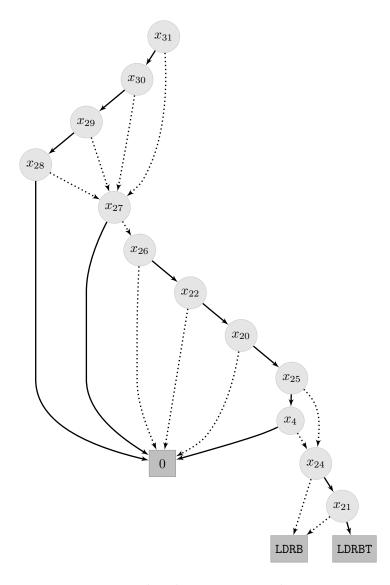

We study how to address the challenges specific to using DBT for full system virtualisation. We start with a fundamental problem in the translator: translations often require an extra register, but such register may not always be available. Our translator therefore needs to spill and restore registers to some location in memory or other hardware that is accessible to the guest. While solving this problem is trivial for process virtualisation, the solution is more involved for system virtualisation, as the hypervisor must write-protect as much of its data structures from the guest as possible, and the guest's data structures cannot be relied upon. We propose new solutions to the spilling problem, and we evaluate their impact on the performance of translated code.

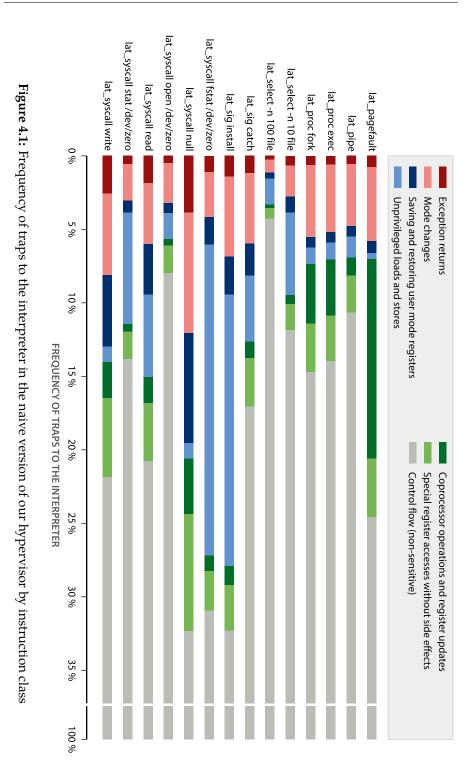

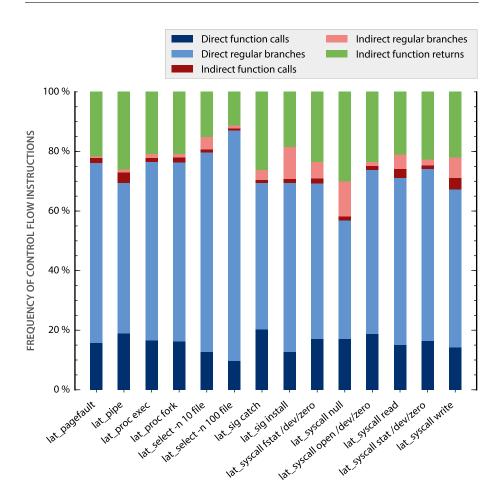

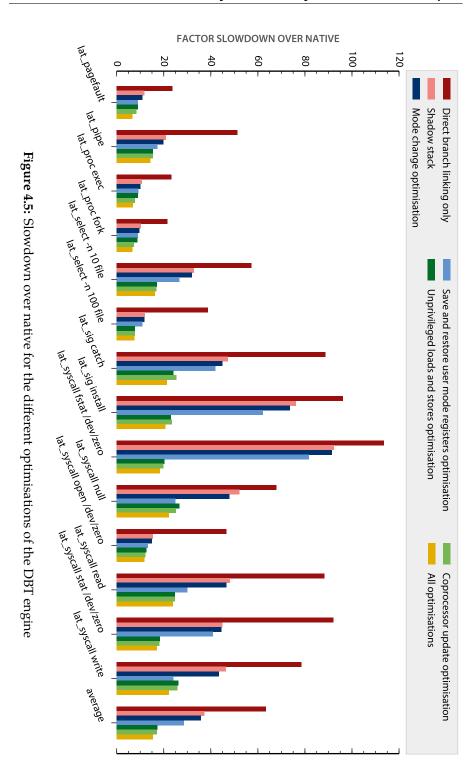

We further analyse the bottlenecks in our DBT engine by running micro-benchmarks from the lmbench suite. Those benchmarks model typical interactions between Linux kernels and their user applications. We study which kinds of system instructions cause a trap from the guest to the hypervisor's DBT engine most frequently, and propose translation techniques to avoid as many of such traps as possible. We analyse the impact of each translation technique separately on each benchmark. As is typical with DBT, much of the run-time overhead can be attributed to control flow, and eliminating traps caused by control flow yields significant speedups. However, we also show that the remaining overhead can be further reduced by 51% on average, by using binary optimisations specific to ARMv7-A system virtualisation.

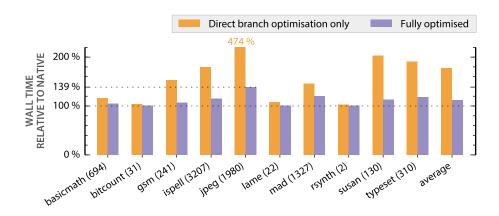

We then compare the run-time virtualisation costs of our optimised DBT engine with our naive, unoptimised DBT engine on real applications. We use benchmarks from the mibench suite to model these applications. We find that a naive configuration of our DBT engine makes the tested applications run up to 5 times slower than native. With our optimisations, however, the maximum perceived slowdown is limited to 39%.

The DBT engine only performs CPU virtualisation. As a hypervisor lives at the lowest level of the software stack, it is also responsible for managing the MMU, the hardware caches and the translation lookaside buffers (TLBs). We therefore discuss how to virtualise the MMU with shadow translation tables, how to virtualise cache operations. We show that guests' cache operations cannot always be applied directly to the hardware caches, because they can cause the hypervisor to lose data.

Our hypervisor makes extensive use of software caches both in the DBT engine and in MMU virtualisation. Such software caches must be kept up to date with the guests' internal state, either through clever memory management or by reusing a guest's hardware cache maintenance operations. The caches of the DBT engine must be updated whenever the guest unmaps, remaps, or modifies code that has already been translated. Similarly, the shadow translation tables must be updated whenever the

guest modifies its translation tables, and in particular when those modifications affect descriptors that have already been shadow mapped.

We have researched both a memory management-based approach and a software cache-based approach for both kinds of software caches. We evaluate our techniques and find that, due to the way cache and TLB organisation works on ARM, shadow translation tables are best managed like a software TLB. The caches of our DBT engine, however, are better managed through memory protection techniques.

During the course of our research, we have designed and implemented a proof-of-concept virtualisation platform for the ARMv7-A architecture to study and evaluate all of the above mentioned techniques. We have demonstrated that using DBT for CPU virtualisation results in acceptable levels of run-time overhead when properly optimised for the target architecture. We have shown how software-only MMU virtualisation can work on ARM, and what the best practices are to manage the shadow translation tables and the caches of the DBT engine. We have hence solved the fundamental challenges to enable software-only virtualisation on ARMv7-A.

# Contents

| A  | cknov  | wledgements                                              | v    |

|----|--------|----------------------------------------------------------|------|

| Ex | kamei  | ncommissie                                               | xi   |

| Le | esco   | mmissie                                                  | xiii |

| N  | ederl  | andstalige samenvatting                                  | xv   |

| Er | nglisł | n summary                                                | xxi  |

| 1  | Intr   | oduction                                                 | 1    |

|    | 1.1    | A brief history of virtualisation                        | 2    |

|    | 1.2    | Taxonomy of hypervisors                                  | 4    |

|    | 1.3    | Virtualisation for embedded systems                      | 7    |

|    | 1.4    | Modern uses of dynamic binary translation                | 10   |

|    | 1.5    | Outline and contributions                                | 12   |

| 2  | For    | mal virtualisation requirements for the ARM architecture | 15   |

|    | 2.1    | Introduction                                             | 16   |

|    | 2.2    | Background and motivation                                | 16   |

|    |        | 2.2.1 Classic virtualisability                           | 16   |

|    |        | 2.2.2 Prior updates to the model                         | 19   |

|    |        | 2.2.3 Advances in computing practice                     | 19   |

|    | 2.3    | An updated model                                         | 22   |

|    |        | 2.3.1 Machine state                                      | 22   |

|    |        | 2.3.2 Address mapping                                    | 23   |

|    |        | 2.3.3 Instruction behaviour                              | 25   |

|    |        | 2.3.4 Events                                             | 27   |

|    |        | 2.3.5 Result                                             | 28   |

|    | 2.4    | Analysis of the ARM architecture                         | 29   |

|    |        | 2.4.1 Machine state                                      | 29   |

|   |      |         |                                                  | 32 |

|---|------|---------|--------------------------------------------------|----|

|   |      | 2.4.3   | Thumb-2 instruction behaviour                    | 34 |

|   |      | 2.4.4   | Conclusion                                       | 35 |

|   | 2.5  | Full v  | irtualisation in practice                        | 35 |

|   |      | 2.5.1   |                                                  | 35 |

|   |      | 2.5.2   | Dynamic binary translation                       | 37 |

|   | 2.6  | Concl   | usions                                           | 40 |

| 3 | The  |         | hypervisor                                       | 41 |

|   | 3.1  |         | luction                                          | 42 |

|   | 3.2  |         | opment history                                   | 43 |

|   | 3.3  |         | evel design                                      | 45 |

|   | 3.4  | MMU     | virtualisation: the memory manager               | 46 |

|   |      | 3.4.1   |                                                  | 47 |

|   |      | 3.4.2   | Shadow translation tables                        | 49 |

|   |      | 3.4.3   | Lazy double shadowing                            | 51 |

|   |      | 3.4.4   | Hypervisor mappings vs. guest mappings           | 52 |

|   | 3.5  | CPU v   | virtualisation: the DBT engine                   | 53 |

|   |      | 3.5.1   | Translation strategies                           | 57 |

|   |      | 3.5.2   | Design choices and limitations                   | 58 |

|   |      | 3.5.3   | Translating PC-sensitive instructions            | 59 |

|   | 3.6  | Excep   | tion handling                                    | 62 |

|   |      | 3.6.1   | Guest mode-dependent exception handling          | 64 |

|   |      | 3.6.2   | Guest exception handling                         | 64 |

| 4 | Eval | luation | of dynamic binary translation techniques         | 67 |

|   | 4.1  | Spillir | ng and restoring registers                       | 68 |

|   |      | 4.1.1   | Lightweight traps                                | 68 |

|   |      | 4.1.2   | 1 0                                              | 70 |

|   | 4.2  | Tackli  | ng DBT-related overhead                          | 71 |

|   |      | 4.2.1   | Control flow                                     | 74 |

|   |      | 4.2.2   | Exception returns and other mode changes         | 77 |

|   |      | 4.2.3   | Saving and restoring user mode registers         | 77 |

|   |      | 4.2.4   | Unprivileged loads and stores                    | 79 |

|   |      | 4.2.5   | Coprocessor operations and register updates      | 80 |

|   |      | 4.2.6   | Special register accesses without side effects   | 81 |

|   |      | 4.2.7   | Summary                                          | 81 |

|   | 4.3  | Evalu   | ation                                            | 82 |

|   |      | 4.3.1   | Register spilling techniques                     | 82 |

|   |      | 4.3.2   | Optimisations to avoid traps to the DBT engine . | 85 |

|     | 4.3.3                                                                                           | Perceived slowdown                                                                                                                                                                                                                                                                                                                                                                                                      | 87                                 |

|-----|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| 4.4 | Concl                                                                                           | usions                                                                                                                                                                                                                                                                                                                                                                                                                  | 89                                 |

|     |                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                         |                                    |

|     |                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                         | 91                                 |

| 5.1 |                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                         | 92                                 |

|     | -                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                         | 92                                 |

|     |                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                         | 94                                 |

|     |                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                         | 94                                 |

| 5.2 |                                                                                                 | ē                                                                                                                                                                                                                                                                                                                                                                                                                       | 95                                 |

|     | -                                                                                               | 0                                                                                                                                                                                                                                                                                                                                                                                                                       | 95                                 |

|     |                                                                                                 | · ·                                                                                                                                                                                                                                                                                                                                                                                                                     | 97                                 |

| 5.3 |                                                                                                 | Ũ                                                                                                                                                                                                                                                                                                                                                                                                                       | 98                                 |

|     |                                                                                                 | , , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                                                                                                                                                                                                                                 | 99                                 |

|     | 5.3.2                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                         | 101                                |

|     | 5.3.3                                                                                           | Handling guest domains                                                                                                                                                                                                                                                                                                                                                                                                  | 101                                |

|     | 5.3.4                                                                                           | Handling guest cache configurations                                                                                                                                                                                                                                                                                                                                                                                     | 104                                |

| 5.4 | DBT c                                                                                           | cache management                                                                                                                                                                                                                                                                                                                                                                                                        | 105                                |

|     | 5.4.1                                                                                           | The memory protection approach                                                                                                                                                                                                                                                                                                                                                                                          | 105                                |

|     | 5.4.2                                                                                           | The software instruction cache approach                                                                                                                                                                                                                                                                                                                                                                                 | 106                                |

| 5.5 |                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                         | 107                                |

|     |                                                                                                 | 5                                                                                                                                                                                                                                                                                                                                                                                                                       | 107                                |

|     | 5.5.2                                                                                           | 0                                                                                                                                                                                                                                                                                                                                                                                                                       | 110                                |

|     | 5.5.3                                                                                           | 0                                                                                                                                                                                                                                                                                                                                                                                                                       | 113                                |

| 5.6 | Concl                                                                                           | usions                                                                                                                                                                                                                                                                                                                                                                                                                  | 115                                |

| Oth | or losse                                                                                        | one learnt                                                                                                                                                                                                                                                                                                                                                                                                              | 117                                |

|     |                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                         | 118                                |

| 0.1 |                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                         | 118                                |

|     |                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                         | 118                                |

|     |                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                         | 119                                |

| 6.2 |                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                         | 120                                |

| 0.1 |                                                                                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                       | 121                                |

|     |                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                         | 124                                |

|     |                                                                                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                       |                                    |

|     | 6.2.4                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                         | 128                                |

|     |                                                                                                 | -                                                                                                                                                                                                                                                                                                                                                                                                                       |                                    |

|     |                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                         | 131                                |

| 7.1 |                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                         | 132                                |

| 7.2 |                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                         | 135                                |

|     | 7.2.1                                                                                           | Scalability                                                                                                                                                                                                                                                                                                                                                                                                             | 135                                |

|     | 7.2.2                                                                                           | DBT engine and memory manager                                                                                                                                                                                                                                                                                                                                                                                           | 136                                |

|     | <b>Trac</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br><b>Oth</b><br>6.1<br>6.2<br><b>Con</b> | 4.4 Concl<br>Trade-offs<br>5.1 Introd<br>5.1.1<br>5.1.2<br>5.1.3<br>5.2 Hardw<br>5.2.1<br>5.2.2<br>5.3 Shado<br>5.3.1<br>5.2.2<br>5.3 Shado<br>5.3.1<br>5.3.2<br>5.3.3<br>5.4 DBT of<br>5.4.1<br>5.4.2<br>5.5 Evalue<br>5.5.1<br>5.5.2<br>5.5.3<br>5.6 Concl<br>Other lesso<br>6.1 Desig<br>6.1.1<br>6.1.2<br>6.1.3<br>6.2 Transl<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Conclusion<br>7.1 Concl<br>7.2 Future<br>7.2.1 | <ul> <li>4.4 Conclusions</li></ul> |

| 7.2.3           | Combining DBT with hardware virtualisation | <br>137 |

|-----------------|--------------------------------------------|---------|

| List of tables  |                                            | 139     |

| List of figures |                                            | 141     |

| List of abbrev  | iations                                    | 143     |

| List of symbol  | s                                          | 147     |

| Bibliography    |                                            | 149     |

#### xxviii

### Chapter 1

### Introduction

The term *virtualisation* is used in many different contexts, ranging from storage and network technologies to execution environments, and even to virtual realities. The research presented in this dissertation focuses on *system virtualisation*—technology that allows multiple operating systems to be executed on the same physical machine simultaneously. It achieves this by isolating those operating systems, also called *guests*, from the physical hardware and from each other, by means of a *hypervisor*.

System virtualisation has already proven itself to be useful in the server and desktop computing worlds. It has many use cases ranging from reducing operational costs of data centres through consolidation, to facilitating software development and emulating legacy software. As embedded systems are growing more and more powerful, and embedded hardware is evolving faster than software, embedded systems can also benefit from virtualisation. Solutions for data centres and desktop computers can, however, not be readily applied to embedded systems, because of differences in requirements, use cases, and architecture.

ARM is by far the leading architecture in the embedded and mobile market [112]. Over the past decade multiple hypervisors have been developed for it. Because the ARM architecture did not support full system virtualisation, most efforts started with paravirtualisation, a technique known to have several drawbacks [39]. Recently, ARM extended its ARMv7-A architecture with hardware support for full virtualisation [13]. While hypervisors using these extensions do not suffer from the drawbacks of paravirtualisation, they cannot run on the vast majority of ARM processors in use today, due to their need for special hardware support.

In this dissertation, we propose generic CPU and memory virtuali-

sation solutions that offer full virtualisation without relying on specific hardware support for the ARMv7-A architecture. To fully virtualise the CPU, we dynamically rewrite the code of guest kernels at run time, a technique known as dynamic binary translation (DBT). As CPU and memory virtualisation are inevitably tied together, we have also researched memory virtualisation techniques based on shadow translation tables.

Prior work on DBT for the ARM architecture mainly focuses on process virtualisation. As system virtualisation comes with its own unique challenges, the existing process virtualisation techniques cannot be used "as is" in the context of full system virtualisation. Furthermore, process virtualisation does not require memory virtualisation. We will therefore propose new solutions to address the challenges of systemlevel DBT on ARM. We have implemented and evaluated our techniques in our own hypervisor, STAR, the first software-only hypervisor that offers full virtualisation using DBT for the ARMv7-A architecture. This hypervisor has been co-developed with The University of Manchester.

The remainder of this chapter provides a concise overview of prior work on system virtualisation in general, and for ARM-based embedded systems. Section 1.1 sketches the origins of virtualisation, and introduces *classic virtualisability*—a theory used to determine whether or not an architecture is suitable for full virtualisation. In Section 1.2, we describe the different techniques for system virtualisation in use today, and discuss their advantages and disadvantages. We use this to classify existing solutions for ARM-based embedded systems in Section 1.3. We illustrate why, even with hardware extensions for virtualisation, DBT-based virtualisation remains useful in Section 1.4. We conclude this chapter in Section 1.5 with an overview of the major contributions and an outline of the remainder of this dissertation.

### **1.1** A brief history of virtualisation

The earliest virtualisation solutions date from the late 1950s and consisted of time sharing systems, created to enable multiple users to use a single machine concurrently [66, 116]. In the early 1960s, IBM engineers working on the M44/44X project first used the word *virtual* in conjunction with computers. They worked on methods to partition the processor time and the memory of an IBM 7044 computer between multiple software images. Those images were referred to as *virtual machines* [44].

The M44/44X predates the inception of modern, third-generation, op-

erating systems with privilege separation and support for multiprogramming. Its virtual machines therefore merely contained the bare minimum abstractions necessary to run individual applications. Operating systems as they are known today only appeared in the early 1960s [29, 38]. The first hypervisor capable of fully virtualising its underlying architecture was IBM's CP-40. It was productised as the CP-67/CMS system and became the first commercial hypervisor at the end of the 1960s [1, 57].

In 1974, Popek and Goldberg [97] defined a set of formal system virtualisation requirements for third-generation computer architectures, based on experiences with virtualisation in contemporary mainframe systems such as the IBM 360/67 (with CP-67/CMS), and the DEC PDP-10. They formally proved that if an architecture meets their requirements, an "efficient" hypervisor can be constructed for that architecture. Their paper is now regarded as one of the groundworks of virtualisation, and their theory is referred to as "classic virtualisability".

Over time, as time-sharing systems replaced batch processing systems, third-generation operating systems matured and took over the role of the old hypervisors: there was no longer a need to run multiple pieces of system software from different users on a single machine; multiple users could run different user-space applications on a single operating system kernel instead. By the early 1980s computer hardware costs had dropped significantly and computers became affordable for the masses. Obsoleted by operating systems, virtualisation was regarded as nothing more but a relic of the past by both industry and academia [30, 105].

Operating systems became more feature-rich, but their complexity also brought stability issues and security concerns. As computer prices kept dropping, it became common practice in industry to dedicate individual machines to specific tasks, effectively reversing the multiprogramming revolution. However, each dedicated system had to be managed independently and most systems were idle most of the time, leading to management overhead and waste of resources. Virtualisation became relevant again, as it was a potential solution to all these problems [105].

Unfortunately, virtualisation techniques originally developed for mainframes could not readily be implemented on most commodity computers and servers: their architecture, the Intel x86, did not meet Popek and Goldberg's strict requirements for efficient hypervisors [2]. In 1999, VMware was the first company to come up with a full virtualisation solution for the x86 architecture using *dynamic binary translation* (DBT) techniques: instructions that made the architecture violate Popek and Goldberg's classic virtualisability requirements were patched at run time in the binary instruction streams of the virtual machines (VMs) [104, 134].

DBT hypervisors are very complex to construct. It did not take long before researchers realised that the problem of virtualising the x86 architecture could also be solved by adapting the operating systems upfront rather than patching them at run time. The hypervisor then presents a customised interface to its VMs, similar but not identical to the underlying hardware. Such techniques are now widely known as *paravirtualisation*; although pioneered by IBM in their early virtualisation work, the term was first coined in 2002 by Whitaker et al. [136, 137] in their work on the Denali hypervisor, the first such hypervisor for the x86 architecture.

Virtualisation, a technology from the mainframe era, quickly conquered the server and desktop markets. By 2005, the trend was picked up by x86 hardware makers Intel and AMD, and the architecture gained hardware support for full virtualisation [3, 127].

### **1.2** Taxonomy of hypervisors

Over the years, many different kinds of virtualisation systems have been designed. The first classification of such systems dates back to 1973. Based on a formal model of how hypervisors interact with the underlying hardware platform, Goldberg [56] defined two types of hypervisors:

- *Type I* hypervisors run directly on top of the hardware, at the highest privilege level. Their guests run at lower privilege levels. These hypervisors are now known as *native* or *bare-metal* hypervisors.

- *Type II* hypervisors run on top of an existing host operating system. They are therefore also referred to as *hosted* hypervisors.

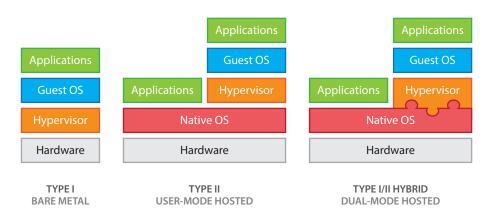

Figure 1.1 depicts the relationships between the hardware, the hypervisor and the operating systems for each type of hypervisor. Type II hypervisors can benefit from the services and abstractions provided by a host operating system. Therefore, the development and debugging processes for such hypervisors are easier than for bare-metal hypervisors: development and debugging tools can be run from the host, essentials such as C libraries and drivers can be reused, and the host can be reused as management interface to the hypervisor. However, not all features of the host are necessary for the hypervisor to operate, and they form a

Figure 1.1: Classification of hypervisors according to Goldberg and Gallard

source of run-time overhead. Such overhead is more easily tolerated on desktop computers and in data centre environments than on resourceconstrained embedded systems. Type I hypervisors avoid the overhead of a host operating system at the expense of more complicated development and debugging processes; furthermore, they require custom run-time libraries and drivers for each hardware platform.

Although modern hypervisors have evolved substantially since the publication of Goldberg's classification, most hypervisors today can be classified as either type I or type I/II hybrids. Gallard et al. [55] have extended Goldberg's formal model to accommodate for such hybrids.

Smith and Nair [113] distinguish between two kinds of hosted hypervisors: *user-mode* hosted hypervisors run fully on top of their host operating system at a lower privilege level than its kernel, while *dual-mode* hosted hypervisors—type I/II hybrids—also contain software components that run at the same privilege level as the host's kernel (such as drivers). Such hybrid designs are necessary for a hosted hypervisor to make use of hardware support for full virtualisation [3, 9, 13, 127].

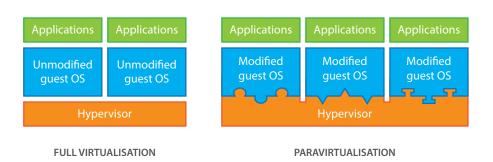

Hypervisors can also be classified based on the techniques they use to virtualise their guests, as shown in Figure 1.2. Firstly, as explained in Section 1.1, we distinguish between *full virtualisation*, also called faithful virtualisation, and *paravirtualisation*. In full virtualisation, a hypervisor presents an interface to its guests that is identical to the underlying hardware platform. Any operating system designed for that hardware platform can then run unmodified as a guest. In theory, guests cannot even distinguish between their virtual copy of the hardware and the real hardware. In practice, the term full virtualisation may also be used for hypervisors that virtualise a physical platform different from the one they run on. A hypervisor based on paravirtualisation presents a modified interface to its guests, which is similar but not identical to the underlying hardware platform. All operating systems must first be adapted to this custom interface before they can be run as a guest [113, 134, 136, 137].

There are many hypervisors based on paravirtualisation and most of them use their own customised interface between the hypervisor and its guests. None of the efforts to standardise those interfaces has gained sufficient momentum to spread to more than a few operating systems or hypervisors [4, 83, 106]. As a consequence, few operating systems support those interfaces out of the box. Instead, hypervisor vendors and third parties must provide source code patch sets to support specific hypervisor interfaces for specific operating system versions. On the one hand, selling and supporting patches constitutes a proper business model for paravirtualisation vendors. On the other hand, paravirtualisation solutions also come with four major drawbacks:

- Developing, maintaining, and testing patch sets for each and every combination of a specific operating system version and a specific hypervisor interface is an expensive process. Although semantic patches may offer a solution to simplify patch management [15, 76, 95], the effort required for testing remains.

- 2. Patched operating systems may exhibit unexpected behaviour because their reliability is not guaranteed and patches may introduce new security issues.

- 3. Licenses may prevent or restrict modifications to operating systems source code, and often impose rules on the distribution of patch sets or patched code.

- 4. Previously certified software stacks will need to be re-certified after patching. The recertification process is expensive and always specific to a particular hypervisor interface, thereby stimulating vendor lock-in.

This analysis is shared by major players in industry including ARM, Nokia and STMicroelectronics [39]. The drawbacks of paravirtualisation can be avoided by using full virtualisation, which comes with the added benefit that it can be used to virtualise a priori unknown software.

Full virtualisation can be achieved either through hardware support or by using software techniques such as DBT. Computer architectures

Figure 1.2: Classification of hypervisors by virtualisation technique

that meet the requirements set out by Popek and Goldberg [97] in 1974 support full virtualisation out of the box. Architectures such as x86 and ARM have gained hardware support for full virtualisation in later iterations through extensions [3, 9, 13, 127]. While hypervisors built for such hardware extensions easily outperform DBT-based hypervisor and are easier to construct, they do not run on older hardware. Furthermore, DBT remains useful in a handful of scenarios, ranging from full-system instrumentation to legacy system software emulation.

### **1.3** Virtualisation for embedded systems

Virtualisation in the server and desktop world has already matured, with both software and hardware solutions available for several years [2, 21, 24, 104, 113, 127, 135]. However, virtualisation of embedded systems is still an area of ongoing research [14, 52, 63]. While the motivation to virtualise embedded systems is similar to desktop and server virtualisation, solutions for the latter cannot be easily reused on embedded systems due to differences in requirements, use cases, and computer architecture.

ARM is by far the leading architecture in the embedded and mobile market [112], and several hypervisors have already been developed for it. A comprehensive overview of the existing solutions is shown in Table 1.1.

Early designs such as ARMvisor [47], B-Labs Codezero Embedded Hypervisor [18], KVM for ARM [40], TRANGO Virtual Processors Hypervisor [122], NEC VIRTUS [73], VirtualLogix VLX [15, 133], VMware MVP [22, 25] and Xen ARM PV [70, 82] all use paravirtualisation, as they predate the introduction of ARM's hardware support for full virtualisation. As stated in Section 1.2, such hypervisors have several drawbacks.

|                                                             | Per i mor | (    |                  |              |

|-------------------------------------------------------------|-----------|------|------------------|--------------|

|                                                             |           |      | Туре             |              |

| Name                                                        | Para      | Full | Goldberg / Smith | References   |

| ARMvisor                                                    | •         | o    | dual-mode hosted | [47]         |

| B-Labs Codezero Embedded Hypervisor                         | •         | 0    | bare-metal       | [18]         |

| ITRI Hypervisor                                             | •         | 0    | dual-mode hosted | [110, 111]   |

| KVM for ARM                                                 | •         | 0    | dual-mode hosted | [40]         |

| KVM/ARM                                                     | 0         | •    | dual-mode hosted | [41, 42]     |

| Open Kernel Labs OKL4 Microvisor                            | •         | •    | bare-metal       | [62–64, 132] |

| Red Bend Software vLogix Mobile                             | 0         | •    | bare-metal       | [102]        |

| SYSGO PikeOS                                                | •         | •    | bare-metal       | [78, 118]    |

| NEC VIRTUS                                                  | •         | 0    | bare-metal       | [73]         |